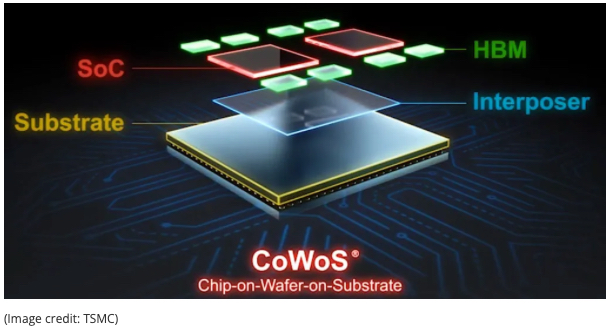

TSMC is pushing the boundaries of chip packaging with its latest iteration of chip-on-wafer-on-substrate (CoWoS) technology, which is set to enable system-in-packages (SiPs) up to nine reticle sizes by 2027. This innovation will support ultra-large processors the size of a human palm, with up to 12 HBM4 memory stacks, catering to the most performance-hungry AI and high-performance computing (HPC) applications. These packages will integrate cutting-edge 1.6nm and 2nm dies, delivering unprecedented transistor density. However, these advancements pose significant challenges for system design, power requirements, and cooling, with demands reaching hundreds of kilowatts per rack and necessitating advanced liquid or immersion cooling solutions.

My Take

TSMC’s 9-reticle CoWoS technology is a big advance in AI and HPC chip design. However, power and cooling challenges will become even more important than they already are for the infrastructure of future data centers.

#TSMC #AI #HPC #Semiconductors #AdvancedPackaging #CoWoS #HBM4 #ChipInnovation #TechTrends

Link to article:

Credit: toms hardware